フロントエンドデザイン

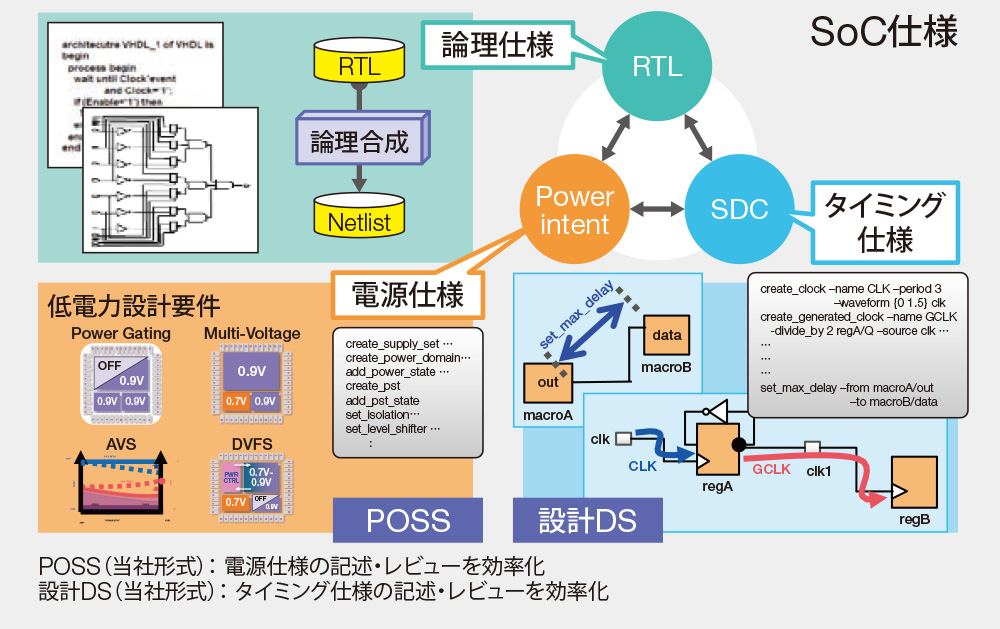

設計仕様インタフェース

SoC設計は、論理設計データのRTLやNetlist以外にも、クロック周波数などのタイミング仕様を記述したSDC、パワーゲーティング設計や多電源・多電圧設計などの電源仕様を記載したCPF/UPFなどのPower Intentが必要です。当社は、SDCやPower Intentの独自形式インタフェースファイルを提供しており、各仕様の記述やレビューの効率化と、ハンドオフされたRTL・電源仕様・タイミング仕様の整合性・レイアウト親和性を素早く検証することを可能にします。

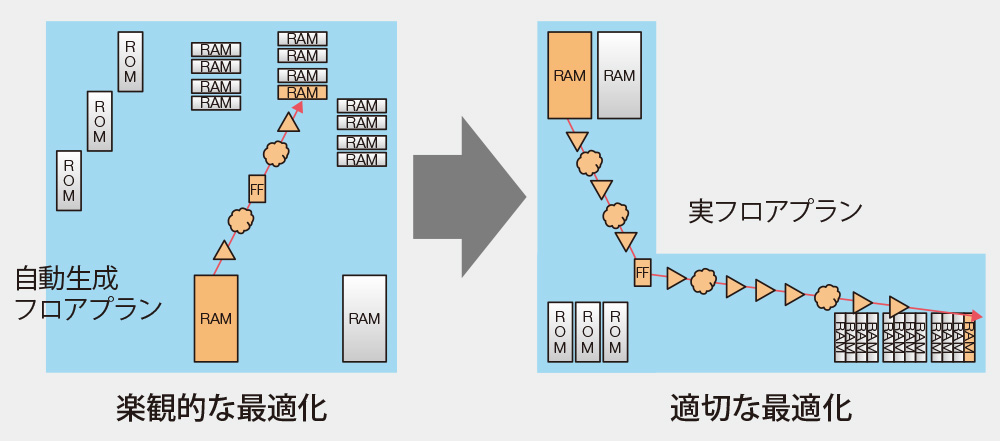

物理考慮論理合成

テクノロジーの微細化に伴い、レイアウトを考慮した論理設計を行うことが、SoC設計の効率化、面積やタイミングの最適化に重要となってきています。このため、当社では実際のレイアウトを考慮して最適化を行う、物理考慮合成を取り入れています。このような論理設計とレイアウト設計の協調により、高機能なSoCを効率的に設計します。