LPB協調設計

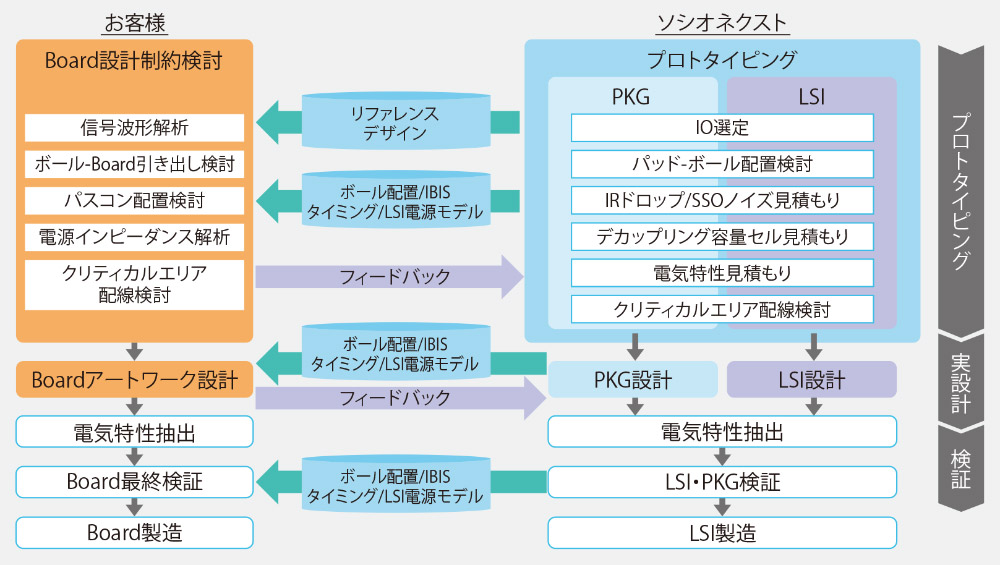

ソシオネクストでは、LPB協調設計フローに基づいたLSI開発を行い、一発完動を実現しています。リファレンスデザインにより設計の見通しを良くするとともに、設計の各段階においてLPB一体解析による全体最適化を可能にすべく、DDR5、LPDDR5などのMemory IFやUSB3.2, PCIe-Gen5などのSerDes IF、および112Gbps PAM-4など超高速IF の伝送路解析に必要なLSIモデル(IBIS、タイミングモデル、LSI電源モデル)を整備しています。これにより、従来は実設計の工程で初めて発見できた問題にプロトタイピング工程で対処することが可能になります。

解析

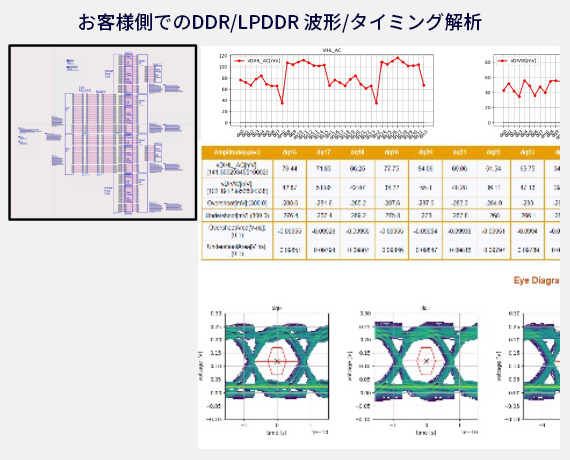

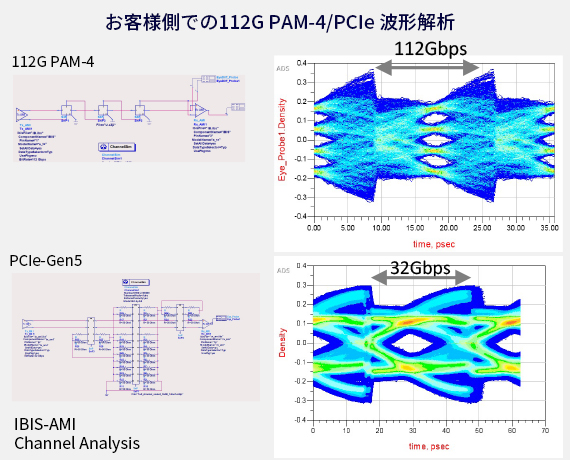

設計初期から、お客様にて波形品質やタイミングを考慮した伝送路解析を実施いただけるよう、IBIS やタイミングモデル(リファレンスデザイン)を提供することが可能です。

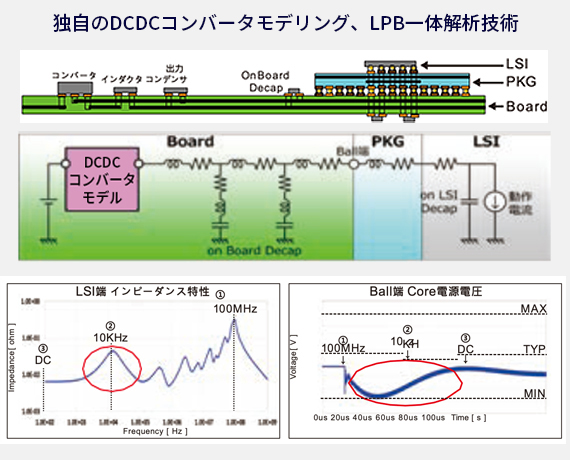

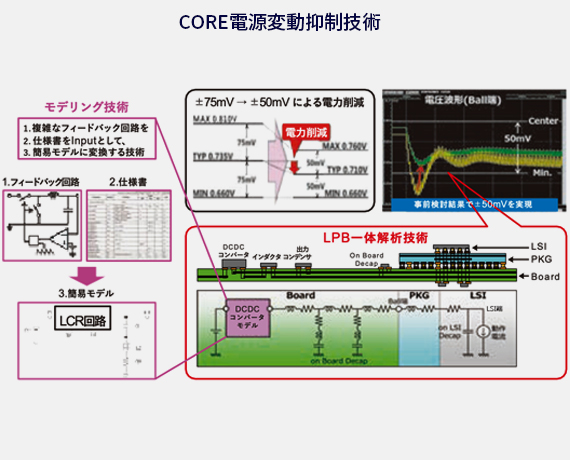

ソシオネクスト独自のDC/DCコンバータモデリング技術およびLPB一体解析技術により、実機現象をノイズ解析で可視化することが可能です。さらに、CORE電源変動抑制技術を組み合わせることで、お客様Boardの低電力化を実現します。

シミュレーション

先進シミュレーション技術を活用し、最適なパッケージソリューションを提供します。

機構シミュレーション

パッケージ設計に機構シミュレーションを取り入れることによって、高信頼性のパッケージ提案が可能です。

[事例:半田接合部の応力解析]

![[事例:半田接合部の応力解析]](images/simulation_02.jpg)

熱設計シミュレーション

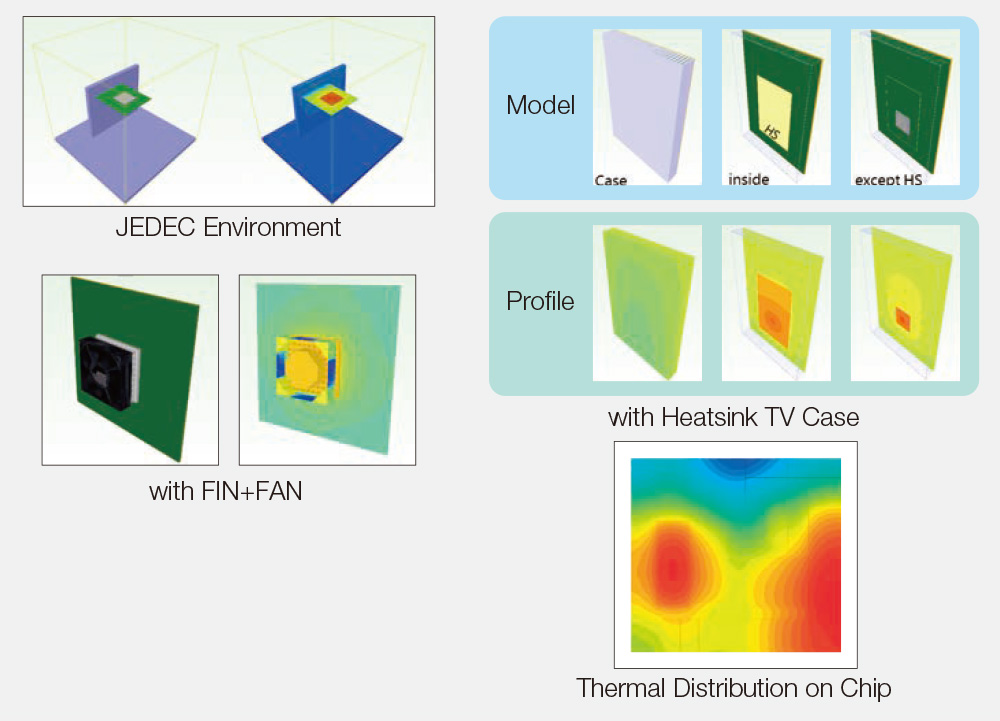

熱抵抗の実測と熱流体シミュレーションの組み合わせにより、製品の使用環境を再現した高精度な熱抵抗解析を実現します。また、JEDEC規格で規定された環境での解析も可能です。

熱抵抗測定

JEDEC規格 JESD51-14に準拠した過渡熱抵抗の実測が可能です。