前端设计

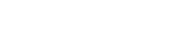

设计规格I/F

在SoC设计中,不单需要逻辑设计数据的RTL和网表,还需要描述了时钟频率等时序规格的SDC、描述电源门控设计、多电源多电压设计等电源规格的CPU/UPF之类的Power Intent。本公司为上述SDC和Power Intent备有独家形式的I/F文档。通过利用这些I/F文档,可以提高描述和研讨各种规格的效率,同时也可迅速验证切换了的RTL、电源规格、时序规格的一致性、布局的亲和力等。

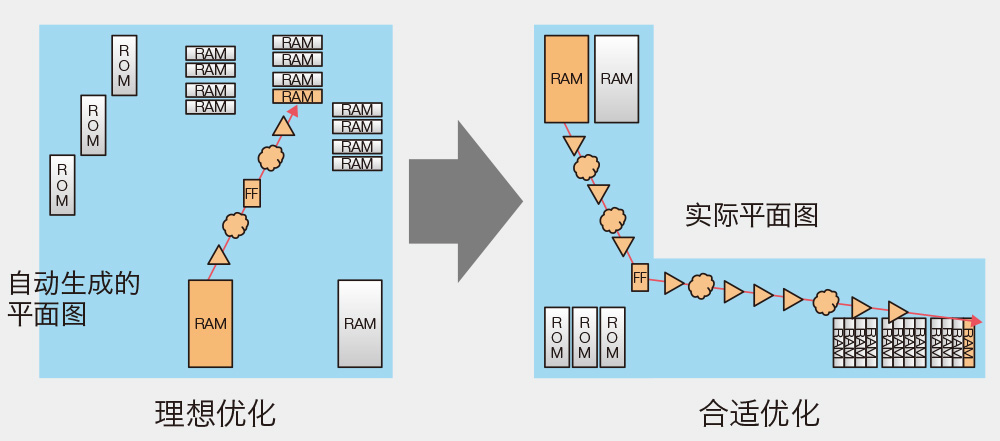

物理考虑逻辑综合

随着技术的进步,就提高SoC设计效率和优化面积和时序而言,考虑到布局的逻辑设计日渐变得重要。因此,本公司采用了物理考虑综合方式,考虑实际布局以进行优化。由于协调了逻辑设计和布局设计,本公司能够有效率地设计高性能SoC。