Front-end Design

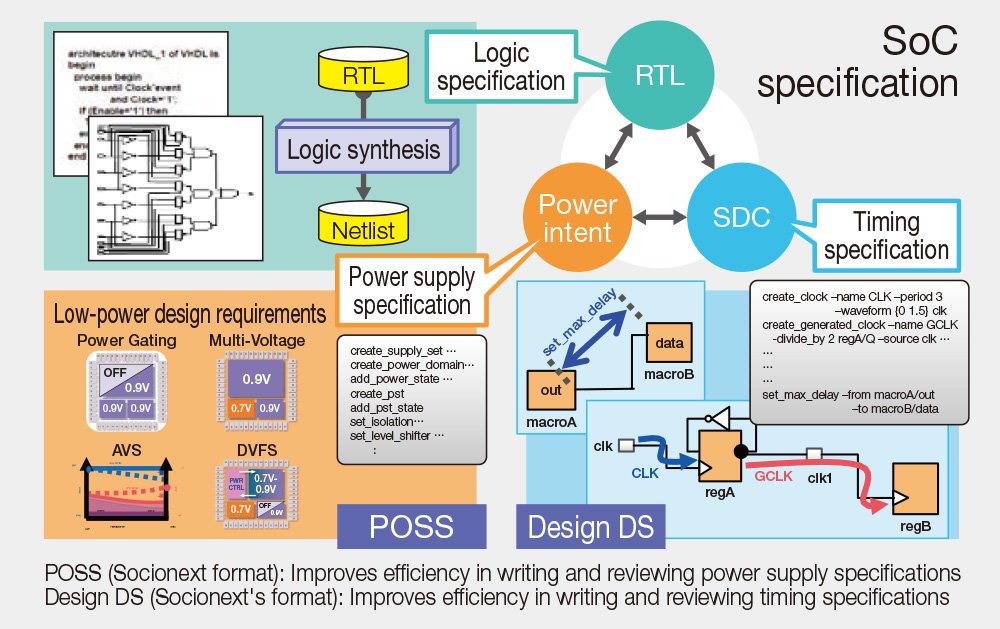

Design Specification Interface

Designing an SoC requires not only RTL and netlist as logic design data, but the power intent, such as the SDC describing timing specifications including clock frequency, and CPF/UPF containing power supply specifications, including power gating design and multi-power/multi voltage design. We provide interface files in our unique format for such SDC and power intent. Using such files allows you to improve efficiency in writing and reviewing specifications and quickly verify the consistency between the handed-off RTL, power supply specifications, and timing specifications as well as layout compatibility.

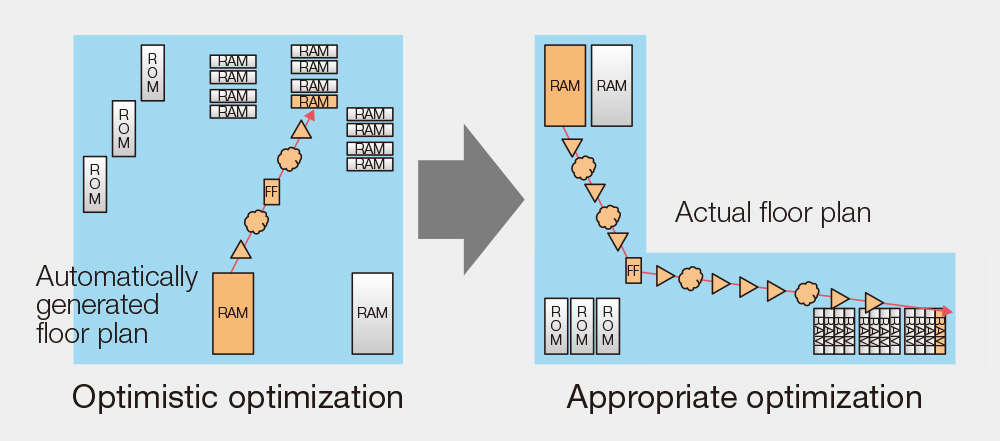

Physical aware Logic synthesis

Due to progress in technology, logic design that takes layout into account is becoming important for improving SoC design efficiency as well as optimizing area and timing. For this reason, we adopt physical aware synthesis that performs optimization by taking the actual layout into account. Through this co-design between the logic design and layout design, we can efficiently design sophisticated SoCs for your product.