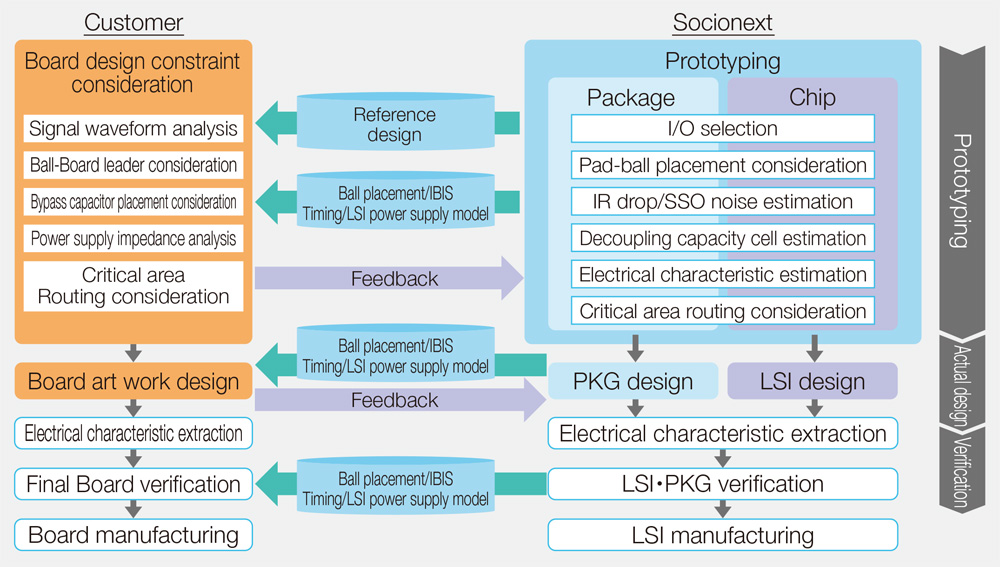

LPB(LSI-Package-Board) co-design

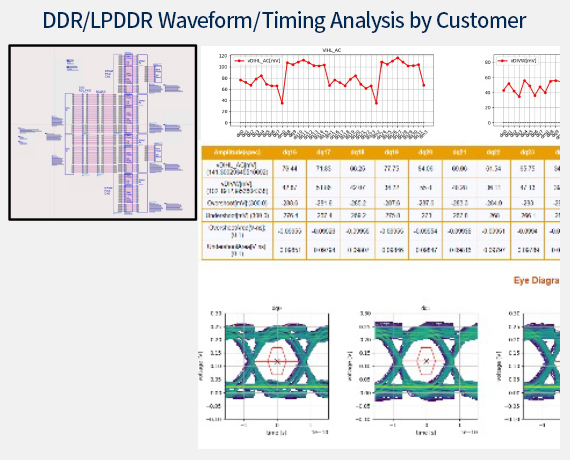

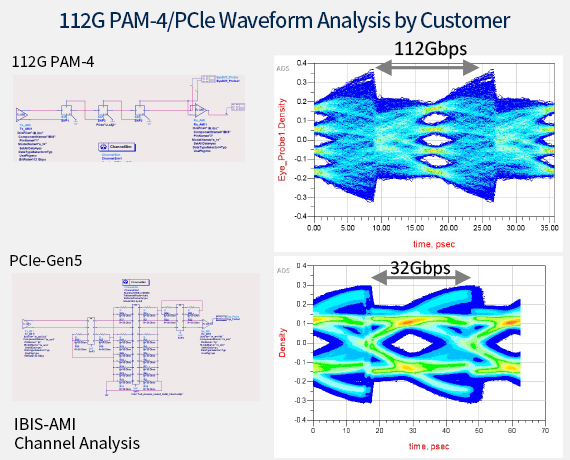

Socionext achieves perfect operation on the first attempt through LSI development based on the LSI-Package-Board (LPB) co-design flow. While improving design forecasting through reference designs, we develop and improve the LSI models (IBIS, timing model, LSI power supply model) necessary for transmission line analysis of DDR5, LPDDR5, and other memory interfaces, as well as USB 3.1, PCIe-Gen3, and other SerDes interfaces, and 112 Gbps PAM-4 and other ultra-high-speed interfaces to achieve total optimization in each design phase based on LPB integrated analysis. This allows issues that in the past would not have emerged until the actual design phase to be addressed in the prototyping phase.

Analysis

We offer customers IBIS and a timing model (reference design) early on in the design stage so that they can conduct transmission line analysis taking waveform quality and timing into account.

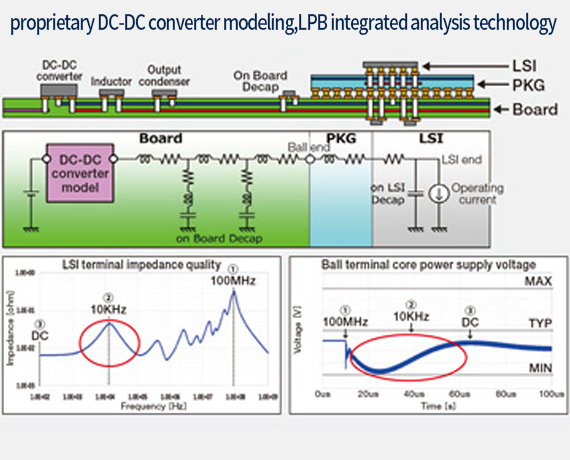

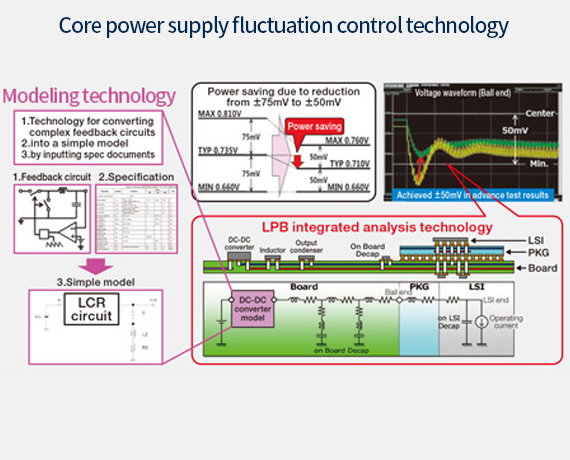

Using Socionext's proprietary DC-DC converter modeling technology and LPB integrated analysis technology, the state of actual equipment can be visualized using noise analysis.

Furthermore, by integrating core power supply fluctuation control technology, customers can achieve low power consumption for their boards.

Simulation

Utilizing advanced simulation technologies, we offer the best package solution.

Mechanism simulation

Incorporating mechanism simulation into package design allows customers to propose high reliability packages.

[Case: Stress Analysis of Solder Joint Sections]

![[Case: Stress Analysis of Solder Joint Sections]](images/simulation_02.jpg)

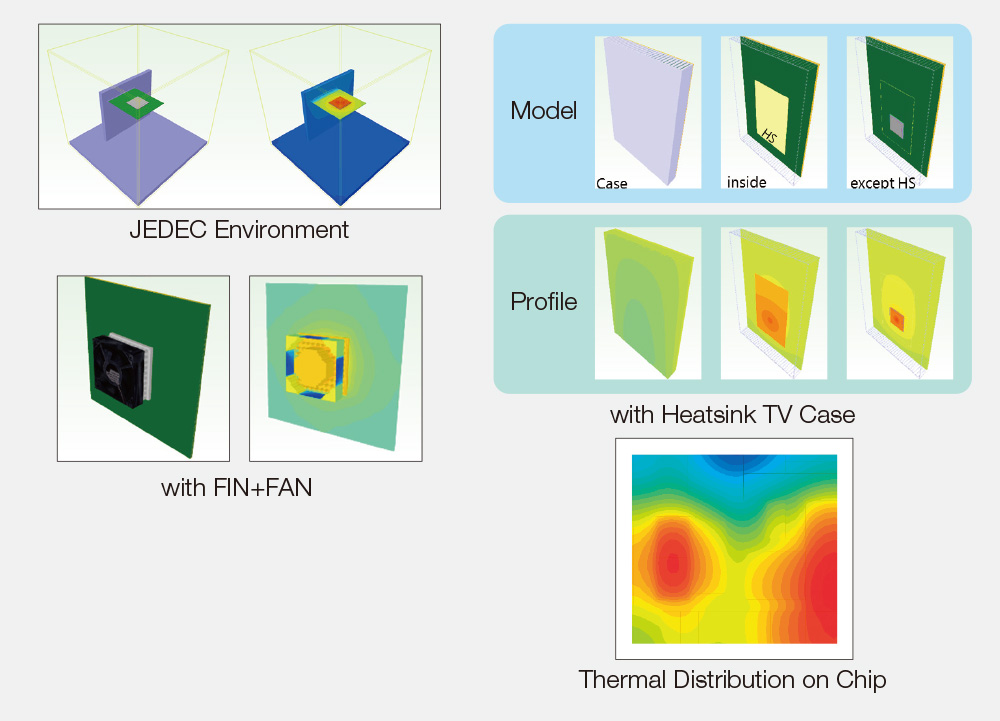

Thermal design simulation

By combining actual measurement of thermal resistors and thermofluid simulation, we perform high accuracy thermal resistance analysis reproducing the operating environment of products. Analysis in an environment defined by the JEDEC standard is also possible.

Thermal resistance measurements

Measurement of transient thermal resistance values in accordance with the JEDEC standard JESD51-14 is possible.