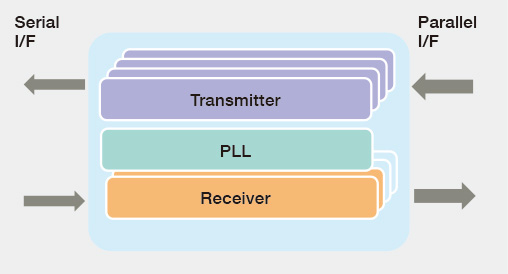

Interface Macro

DDR Interface

Socionext provides various DDR interface macros from low-to-middle speed forwarding bandwidth to high-speed forwarding bandwidth or low power, with various process technologies. Moreover, we support development for signal quality and cost optimization through design support by Chip-Package-Board co-design.

[DDR Interface Configuration Diagram]

![[DDR Interface Configuration Diagram]](images/interface_01.jpg)

DDR Interface macros

High-speed/ high-bandwidth:DDR

Low Power:LPDDR

Broadband:HBM

Compatible with many different DRAM configurations and PKG options, such as Fly-by, PoP, and DIMM thanks to the PHY function (training function).

DDR interface design support (Chip–Package–Board codesign)

Timing verification : Verifies the timing of all DDR-IF systems including delays between LSI I/O and DRAM

Power Integrity : Optimizes the parasitic inductance, resonant frequency, and power supply (PKG, PCB) impedance as part of the power supply impedance design

Signal Integrity : Optimizes Driver strength, terminator resistance, and interconnect topology

Bus switching verification: Optimizes write and read bus switch timing

![[LPDDR4 3733 DQ Waveforms]](images/interface_002.jpg)

MIPI Interface

This high-speed interface is used to build a camera and display system by combining high-speed, high resolution CMOS image sensors. This interface provides a solution for highly expressive images.

MIPI C/D-PHY macro

Transmission speed C-PHY 3.5Gsps(8Gbps) @ 1lane

Transmission speed D-PHY 4.5Gbps @ 1lane

C-PHY Rx reception tolerance test waveform

PCI Express Interface

As a result of the recent rapid improvement in CPU processing capability and an increase in the need for high-capacity data transfer, it has become extremely difficult to achieve the expected system performance with existing buses. The PCI Express interface used by Socionext overcomes these problems by being able to deliver data transfer rates in the hundreds of megabytes.

PCI Express Evaluation Environment

![[PCI Express Evaluation Environment]](images/interface_07.jpg)

PCI Express output waveform @32 Gbps

![[PCI Express output waveform @32 Gbps]](images/interface_07_2.jpg)

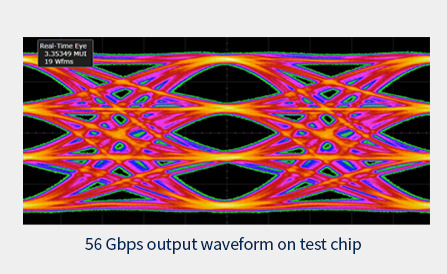

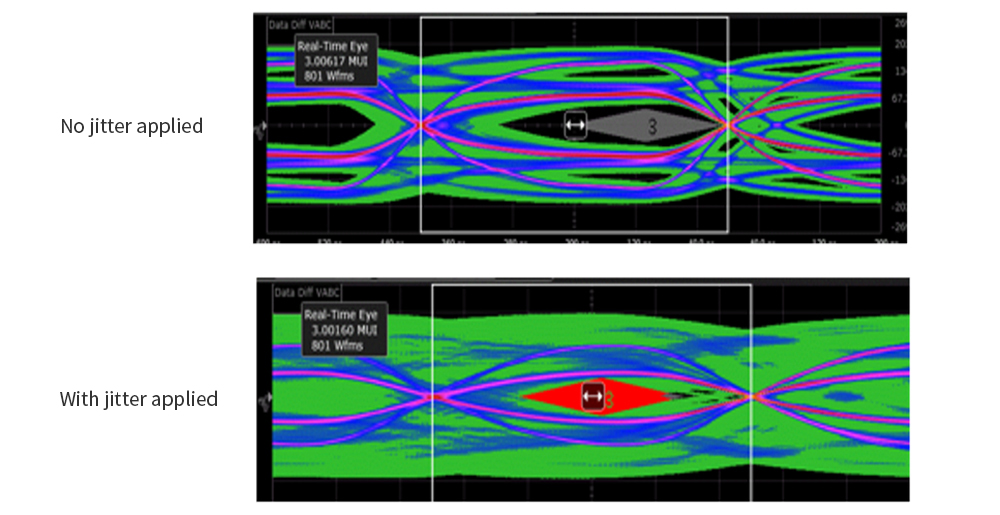

1G-56Gbps SerDes Interface

With transmission performance of 1 Gbps to 56.4 Gbps per lane and a configuration comprised of multiple channels, we provide a high-performance SerDes macro for constructing 100G/200G/400G optical networks or 100G Ether systems.

The built-in low-jitter, high-performance PLL enables robust transmission up to 28 Gbps per lane (PAM4 56 Gbps). Support is available for a wide range of standards, including OIF-CEI-11G-SR, OIF-CEI-28G-SR, OIF-CEI-28G-VSR, OIF-CEI-56G-VSR, IEEE802.3ba CAUI, IEEE802.3bm CAUI4, and XFI and so forth.